# W6692

# **PCI Bus ISDN S/T-Controller**

# **Data Sheet**

The information described in this document is the exclusive intellectual property of Winbond Electronics Corp and shall not be reproduced without permission from Winbond.

Winbond is providing this document only for reference purposes for W6692-based system design. Winbond assumes no responsibility for errors or omissions. All data and specifications are subject to change without notice.

# TABLE OF CONTENTS

| 1. GENERAL DESCRIPTION                                                                                               | 9  |

|----------------------------------------------------------------------------------------------------------------------|----|

| 2. FEATURES                                                                                                          | 9  |

| 3. PIN CONFIGURATION                                                                                                 | 10 |

| 4. PIN DESCRIPTION                                                                                                   | 13 |

| 5. SYSTEM DIAGRAM AND APPLICATIONS                                                                                   | 16 |

| 6. BLOCK DIAGRAM                                                                                                     | 17 |

| 7. FUNCTIONAL DESCRIPTIONS                                                                                           |    |

| 7.1 Main Block Functions                                                                                             |    |

| 7.2 Layer 1 Functions Descriptions                                                                                   |    |

| 7.2.1 S/T Interface Transmitter/Receiver                                                                             |    |

| 7.2.2 Receiver Clock Recovery And Timing Generation                                                                  |    |

| 7.2.3 Layer 1 Activation/Deactivation.                                                                               |    |

| <ul><li>7.2.3.1 States Descriptions And Command/Indication Codes</li><li>7.2.3.2 State Transition Diagrams</li></ul> |    |

| 7.2.4 D Channel Access Control                                                                                       |    |

| 7.2.4 D Chainel Access Control                                                                                       |    |

| 7.2.5.1 FAinfA_1fr                                                                                                   |    |

| 7.2.5.2 FAinfB_1fr                                                                                                   |    |

| 7.2.5.3 FAinfD_1fr                                                                                                   |    |

| 7.2.5.4 FAinfA_kfr                                                                                                   |    |

| 7.2.5.5 FAinfB_kfr                                                                                                   |    |

| 7.2.5.6 FAinfD_kfr                                                                                                   |    |

| 7.2.5.7 Faregain                                                                                                     |    |

| 7.2.6 Multiframe Synchronization                                                                                     |    |

| 7.2.7 Test Functions                                                                                                 |    |

| 7.3 Serial Interface Bus                                                                                             |    |

| 7.4 B Channel Switching                                                                                              |    |

| 7.5 PCM Port                                                                                                         | 40 |

| 7.6 D Channel HDLC Controller                                                                                        | 40 |

| 7.6.1 D Channel Message Transfer Modes                                                                               | 41 |

| 7.6.2 Reception of Frames in D Channel                                                                                                                                              | 41 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 7.6.3 Transmission of Frames in D Channel                                                                                                                                           | 42 |

| 7.7 B Channel HDLC Controller                                                                                                                                                       | 13 |

| 7.7.1 Reception of Frames in B Channel                                                                                                                                              |    |

| 7.7.2 Transmission of Frames in B Channel                                                                                                                                           |    |

|                                                                                                                                                                                     |    |

| 7.8 GCI Mode Serial Interface Bus                                                                                                                                                   |    |

| 7.8.1 GCI Mode C/I0 Channel Handling                                                                                                                                                |    |

| 7.8.2 GCI Mode Monitor Channel Handling                                                                                                                                             | 46 |

| 7.9 PCI/MP Interface Circuit                                                                                                                                                        | 48 |

| 7.9.1 PCI Slave Mode And Configuration Serial EEPROM                                                                                                                                |    |

| 7.9.2 8-bit Microprocessor Interface                                                                                                                                                | 49 |

| 7.10 Peripheral Control                                                                                                                                                             | 49 |

|                                                                                                                                                                                     |    |

| 8. REGISTER DESCRIPTIONS                                                                                                                                                            | 51 |

| 8.1 Chip Control and D_ch HDLC controller                                                                                                                                           |    |

| 8.1.1 D_ch receive FIFO D_RFIFO Read Address 00H/00H                                                                                                                                |    |

| 8.1.2 D_ch transmit FIFO D_XFIFO Write Address 04H/01H                                                                                                                              |    |

| 8.1.3 D_ch command register D_CMDR Read/Write Address 08H/02H                                                                                                                       |    |

| 8.1.4 D_ch Mode Register D_MODE Read/Write Address 0CH/03H                                                                                                                          |    |

| 8.1.5 Timer 1 Register TIMR1 Read/Write Address 10H/04H                                                                                                                             |    |

| 8.1.6 Interrupt Status Register ISTA Read_clear Address 14H/05H                                                                                                                     |    |

| 8.1.7 Interrupt Mask Register IMASK R/W Address 18H/06H                                                                                                                             |    |

| 8.1.8 D_ch Extended Interrupt Register D_EXIR Read_clear Address 1CH<br>8.1.9 D_ch Extended Interrupt Mask Register D_EXIM Read/Write Address 20H/08H                               |    |

| 8.1.10 D_ch Status Register D_XSTA Read Address 24H/09H                                                                                                                             |    |

| 8.1.10 D_ch Receive Status Register D_RSTA Read Address 241/0911                                                                                                                    |    |

| 8.1.12 D_ch SAPI Address Mask D_SAM Read/Write Address 20H/0BH                                                                                                                      |    |

| 8.1.13 D_ch SAPI1 Register D_SAP1 Read/Write Address 30H/0CH                                                                                                                        |    |

| 8.1.14 D ch SAPI2 Register D SAP2 Read/Write Address 34H/0DH                                                                                                                        |    |

| 8.1.15 D_ch TEI Address Mask D_TAM Read/Write Address 38H/0EH                                                                                                                       |    |

| 8.1.16 D_ch TEI1 Register D_TEI1 Read/Write Address 3CH/0FH                                                                                                                         |    |

| 8.1.17 D_ch TEI2 Register D_TEI2 Read/Write Address 40H/10H                                                                                                                         |    |

| 8.1.18 D_ch Receive Frame Byte Count High D_RBCH Read Address 44H/11H                                                                                                               | 61 |

| 8.1.19 D_ch Receive Frame Byte Count Low D_RBCL Read Address 48H/12H                                                                                                                | 62 |

| 8.1.20 Timer 2 TIMR2 Write Address 4CH/13H                                                                                                                                          | 62 |

| 8.1.21 Layer 1_Ready Code L1_RC Read/Write Address 50H/14H                                                                                                                          | 62 |

| 8.1.22 Control Register CTL Read/Write Address 54H/15H                                                                                                                              |    |

| 8.1.23 Command/Indication Receive Register CIR Read Address 58H/16H                                                                                                                 |    |

| 8.1.24 Command/Indication Transmit Register CIX Read/Write Address 5CH/17H                                                                                                          |    |

| 8.1.25 S/Q Channel Receive Register SQR Read Address 60H/18H                                                                                                                        |    |

| 8.1.26 S/Q Channel Transmit Register SQX Read/Write Address 64H/19H                                                                                                                 |    |

| 8.1.27 Peripheral Control Register PCTL Read/Write Address 68H/1AH                                                                                                                  |    |

| 8.1.28 Monitor Receive Channel 0 MOOR Read Address 6CH/1BH                                                                                                                          |    |

| 8.1.29 Monitor Transmit Channel 0 MOOX Read/Write Address 70H/1CH                                                                                                                   |    |

| <ul> <li>8.1.30 Monitor Channel 0 Interrupt Register MO0I Read_clear Address 74H/1DH</li> <li>8.1.31 Monitor Channel 0 Control Register MO0C- Read/Write Address 78H/1EH</li> </ul> |    |

| 0.1.31 MONTO CHAINEL CONTO RESIST MOUC REAL WHITE AUTESS / ON/ IER                                                                                                                  | 0/ |

| W6692 PCI ISDN S/T                                                              | '-Controller |

|---------------------------------------------------------------------------------|--------------|

| 8.1.32 GCI Mode Control/Status Register GCR Read/Write Address 7CH/1FH          | 68           |

| 8.1.33 Peripheral Address Register XADDR Read/Write Address F4H/3DH             |              |

| 8.1.34 Peripheral Data Register XDATA Read/Write Address F8H/3EH                | 70           |

| 8.1.35 Serial EEPROM Control Register EPCTL Read/Write Address FCH/3FH          |              |

| 8.1.36 Monitor Receive Channel 1 Register MO1R Read Address 6DH/40H             | 71           |

| 8.1.37 Monitor Transmit Channel 1 MO1X Read/Write Address 71H/41H               | 72           |

| 8.1.38 Monitor Channel 1 Interrupt Register MO1I Read_clear Address 75H/42H     |              |

| 8.1.39 Monitor Channel 1 Control Register MO1C Read/Write Address 79H/43H       | 72           |

| 8.1.40 GCI IC1 Receive Register IC1R Read Address 6EH/44H                       |              |

| 8.1.41 GCI IC1 Transmit Register IC1X Read/Write Address 72H/45H                |              |

| 8.1.42 GCI IC2 Receive Register IC2R Read Address 6FH/46H                       |              |

| 8.1.43 GCI IC2 Transmit Register IC2X Read/Write Address 73H/47H                |              |

| 8.1.44 GCI CI1 Indication Register CI1R Read Address 7DH/48H                    |              |

| 8.1.45 GCI CI1 Command Register CI1X Read/Write Address 7EH/49H                 |              |

| 8.1.46 GCI Extended Interrupt Register GCI_EXIR Read_clear Address 76H/4AH      | 74           |

| 8.1.47 GCI Extended Interrupt Mask Register GCI_EXIM Read/Write Address 7AH/4BH | 75           |

| 8.2 B1 HDLC controler                                                           | 75           |

| 8.2.1 B1 ch receive FIFO B1 RFIFO Read Address 80H/20H                          |              |

| 8.2.2 B1_ch transmit FIFO B1_XFIFO Write Address 84H/21H                        |              |

| 8.2.3 B1_ch command register B1_CMDR Read/Write Address 88H/22H                 |              |

| 8.2.4 B1_ch Mode Register B1_MODE Read/Write Address 8CH/23H                    |              |

| 8.2.5 B1_ch Extended Interrupt Register B1_EXIR Read_clear Address 90H/24H      |              |

| 8.2.6 B1_ch Extended Interrupt Mask Register B1_EXIM Read/Write Address 94H/25H |              |

| 8.2.7 B1_ch Status Register B1_STAR Read Address 98H/26H                        | 80           |

| 8.2.8 B1_ch Address Mask Register 1 B1_ADM1 Read/Write Address 9CH/27H          |              |

| 8.2.9 B1_ch Address Mask Register 2 B1_ADM2 Read/Write Address A0H/28H          |              |

| 8.2.10 B1_ch Address Register 1 B1_ADR1 Read/Write Address A4H/29H              |              |

| 8.2.11 B1_ch Address Register 2 B1_ADR2 Read/Write Address A8H/2AH              |              |

| 8.2.12 B1_ch Receive Frame Byte Count Low B1_RBCL Read Address ACH/2BH          |              |

| 8.2.13 B1_ch Receive Frame Byte Count High B1_RBCH Read Address B0H/2CH         |              |

| 8.2.14 B1_ch Transmit Idle Pattern B1_IDLE Read/Write Address B4H/2DH           |              |

|                                                                                 |              |

| 8.3 B2 HDLC controller                                                          |              |

| 8.4 PCI Configuration Register                                                  | 84           |

| 8.4.1 Device/Vendor ID Register Read Address 00 <sub>H</sub>                    | 85           |

| 8.4.2 Status/Command Register Read/Write Address 04 <sub>H</sub>                |              |

| 8.4.3 Class Code/Revision ID Register Read Address 08 <sub>H</sub>              |              |

| 8.4.4 Header Type/Latency Timer Register Read Address 0C <sub>H</sub>           |              |

| 8.4.5 Base Address Register 0 Read/Write Address 10 <sub>H</sub>                |              |

| 8.4.6 Base Address Register 1 Read/Write Address $14_{\rm H}$                   |              |

| 8.4.7 Subsystem/Subsystem Vendor ID Register Read Address $2C_{H}$              |              |

| 8.4.8 Interrupt Line Register Read/Write Address $3C_{H}$                       |              |

| 8.4.9 Capability Pointer Read Address $34_{\text{H}}$                           |              |

| 8.4.10 Power Management Capability Read Address $40_{\rm H}$                    |              |

| 8.4.11 Power Management Capability Read Address 40 <sub>H</sub>                 |              |

| 0.7.11 Fower Management Control/Status Read, white Address 77H                  |              |

| 9. ELECTRICAL CHARACTERISTICS                                                   | 94           |

|                                                                                 |              |

| Absolute Maximum Rating94 |

|---------------------------|

|---------------------------|

| 9.2 Power Supply                                                                                                                                   |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9.3 DC Characteristics                                                                                                                             |  |

| <ul> <li>9.4 Preliminary Switching Characteristics</li> <li>9.4.1 PCM Interface Timing<sup>1)</sup></li> <li>9.4.2 Serial EEPROM Timing</li> </ul> |  |

| 9.4.1 PCM Interface Timing <sup>1)</sup>                                                                                                           |  |

| 9.4.2 Serial EEPROM Timing                                                                                                                         |  |

| 9.4.3 Peripheral Interface Timing                                                                                                                  |  |

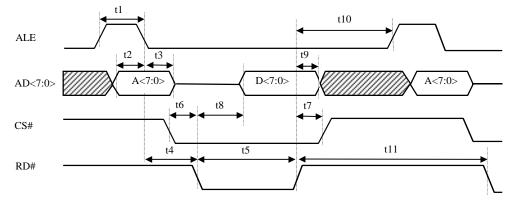

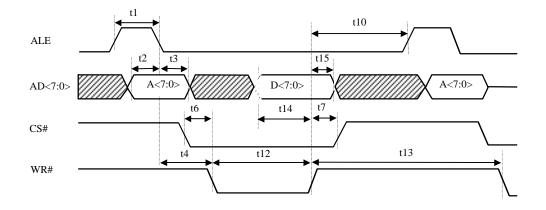

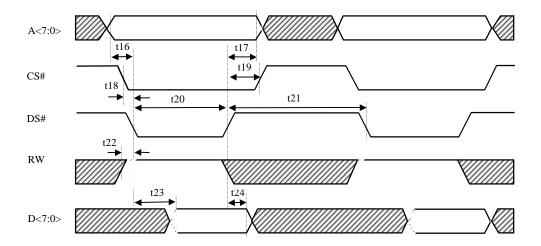

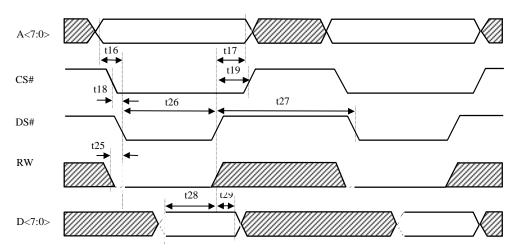

| 9.4.5 8-bit Microprocessor Timing                                                                                                                  |  |

| 9.5 AC Timing Test Conditions                                                                                                                      |  |

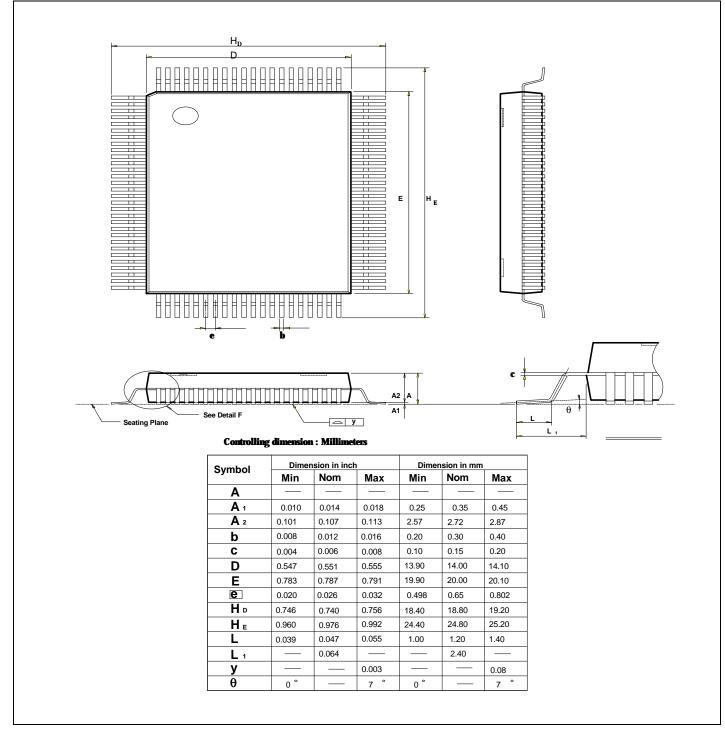

| 10. PACKAGE SPECIFICATIONS                                                                                                                         |  |

# LIST OF FIGURES

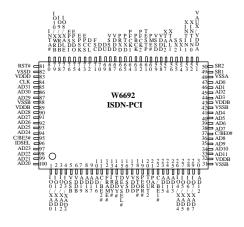

| FIG.3.1 W6692 PIN CONFIGURATION - PCI MODE                           | 10 |

|----------------------------------------------------------------------|----|

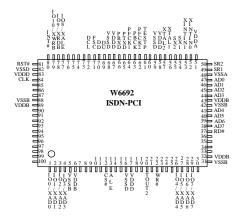

| FIG.3.2 W6692 PIN CONFIGURATION - INTEL BUS MODE                     | 11 |

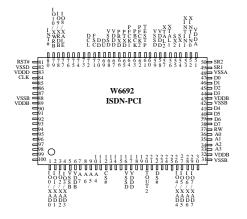

| FIG.3.3 W6692 PIN CONFIGURATION - MOTOROLA BUS MODE                  | 12 |

| FIG.5.1 ISDN INTERNET PASSIVE S-CARD WITH TWO POTS CONNECTIONS       | 16 |

| FIG.6.1 W6692 FUNCTIONAL BLOCK DIAGRAM                               | 17 |

| FIG.7.1 FRAME STRUCTURE AT S/T INTERFACE                             | 20 |

| FIG.7.2 W6692 WIRING CONFIGURATION IN TE APPLICATIONS                |    |

| FIG.7.3 EXTERNAL TRANSMITTER CIRCUITRY                               |    |

| FIG.7.4 EXTERNAL RECEIVER CIRCUITRY                                  | 22 |

| FIG.7.5 LAYER 1 ACTIVATION/DEACTIVATION STATE DIAGRAM - NORMAL MODE  | 28 |

| FIG.7.6 LAYER 1 ACTIVATION/DEACTIVATION STATE DIAGRAM - SPECIAL MODE | 29 |

| FIG.7.7 SSP AND SCP TEST SIGNALS                                     |    |

| FIG 7.8 GCI MODE CHANNEL STRUCTURE                                   |    |

| FIG.7.9 SERIAL EEPROM DATA LAYOUT                                    | 48 |

### LIST OF TABLES

| TABLE 4.1 W6692 PIN DESCRIPTIONS                                   |    |

|--------------------------------------------------------------------|----|

| TABLE 7.1 OUTPUT PHASE DELAY COMPENSATION TABLE                    | 24 |

| TABLE 7.2 LAYER 1 COMMAND CODES                                    | 26 |

| TABLE 7.3 LAYER 1 INDICATION CODES                                 |    |

| TABLE 7.4 D PRIORITY CLASSES                                       |    |

| TABLE 7.5 D PRIORITY COMMANDS/INDICATIONS                          |    |

| TABLE 7.6 MULTIFRAME STRUCTURE IN S/T INTERFACE                    | 35 |

| TABLE 8.1 REGISTER ADDRESS MAP : CHIP CONTROL AND D CHANNEL HDLC   | 51 |

| TABLE 8.2 REGISTER SUMMARY :       CHIP CONTROL AND D CHANNEL HDLC |    |

| TABLE 8.3 REGISTER ADDRESS MAP : B1 CHANNEL HDLC                   | 75 |

| TABLE 8.4 REGISTER SUMMARY : B1 CHANNEL HDLC                       | 76 |

| TABLE 8.5 REGISTER ADDRESS MAP : B2 CHANNEL HDLC                   | 83 |

| TABLE 8.6 REGISTER SUMMARY : B2 CHANNEL HDLC                       | 83 |

| TABLE 8.7       PCI CONFIGURATION SPACE                            |    |

# **1. GENERAL DESCRIPTION**

The Winbond's single chip PCI bus ISDN S/T interface controller (W6692) is an all-in-one device suitable for ISDN Internet access. Three HDLC controllers are incorporated in the chip, one for D channel and the other two for B channels. These HDLC controllers facilitate efficient access to signaling and data services. The PCM codec interface provides voice service or other services. The built in PCI 2.2 interface circuit makes glueless design for PCI bus add-on card application.

### **2. FEATURES**

- \* Full duplex 2B + D S/T-interface transceiver compliant with ITU-T I.430 Recommendation

- \* One D channel HDLC controller

- Maskable address recognition

- Transparent (HDLC) mode

- FIFO buffer (2 x 128 bytes)

- \* Two B channel HDLC controllers

- Maskable address recognition

- Bit rate options : 56 or 64 kbps

- Transparent (HDLC mode) or extended transparent mode (clear channel)

- FIFO buffer (2 x 128 bytes) per B channel

- \* Two PCM codec interfaces for speech and POTS application

- \* Various B channel switching capabilities

- \* GCI master/slave interface

- \* Built in PCI 2.2 slave mode circuit

- \* ACPI capability : PCI 2.2 and PCI Power Management 1.1 compliant

- \* Serial EEPROM interface for PCI configuration

- \* Peripheral control pins

- \* 8-bit microprocessor interface when PCI is disabled for TA application

- \* Digital : 5V or 3.3V, analog : 5V

- \* Advanced CMOS technology

- \* Low power consumption

- \* 100-pin QFP package

# **3. PIN CONFIGURATION**

# FIG.3.1 W6692 PIN CONFIGURATION - PCI MODE

### FIG.3.2 W6692 PIN CONFIGURATION - INTEL BUS MODE

### FIG.3.3 W6692 PIN CONFIGURATION - MOTOROLA BUS MODE

# **4. PIN DESCRIPTION**

### **TABLE 4.1 W6692 PIN DESCRIPTIONS**

Notation : The suffix **"#"** indicates an active LOW signal.

| Pin           | Pin                                                                                                                   | Туре         | Functions                                                                                                                                                                                                                                                                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name          | Number                                                                                                                | • -          |                                                                                                                                                                                                                                                                                                                                               |

|               |                                                                                                                       |              | PCI Bus                                                                                                                                                                                                                                                                                                                                       |

| CLK           | 84                                                                                                                    | Ι            | <ul> <li>PCI Mode : PCI Clock. All other PCI signals, except RST#, INTA# are sampled on the rising edge of CLK. According to PCI 2.1/2.2 specification, CLK is stable at least 100 μs (Trst-clk) before deassertion of RST#.</li> <li>Intel Bus Mode : Must be pulled to HIGH.</li> <li>Motorola Bus Mode : Must be pulled to LOW.</li> </ul> |

| AD31-AD0      | 85,86,87,90,91,<br>92,93,94,97,98,<br>99,100,7,8,9,10,<br>23,24,25,30,33,<br>34,35,36,38,39,<br>40,41,44,45,46,<br>47 | I/O          | Address and Data are multiplexed on the same PCI pins. During the address phase, AD31-0 contain a 32-bit physical address. During the data phase, AD7-AD0 contain the least significant byte and AD31-AD24 contain the most significant byte.                                                                                                 |

| C/BE3#-C/BE0# | 95,11,22,37                                                                                                           | Ι            | Bus command and Byte Enables.<br>During the address phase of a transaction, they define the bus<br>command.<br>During data phase, they are used as Byte Enables.                                                                                                                                                                              |

| PAR           | 21                                                                                                                    | I/O          | Parity is even parity across AD31-AD0 and C/BE3#-C/BE0#.                                                                                                                                                                                                                                                                                      |

| FRAME#        | 12                                                                                                                    | Ι            | FRAME# is asserted to indicate a bus transaction is beginning.                                                                                                                                                                                                                                                                                |

| TRDY#         | 14                                                                                                                    | 0            | Target Ready indicates W6692 is able to complete the current data phase of the transaction.                                                                                                                                                                                                                                                   |

| IRDY#         | 13                                                                                                                    | Ι            | Initiator Ready indicates the bus master's ability to complete the current data phase of the transaction.                                                                                                                                                                                                                                     |

| STOP#         | 18                                                                                                                    | 0            | Stop indicates W6692 is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                |

| DEVSEL#       | 15                                                                                                                    | 0            | Device Select indicates W6692 has decoded itself as the target of the current access.                                                                                                                                                                                                                                                         |

| IDSEL         | 96                                                                                                                    | Ι            | Initialization Device Select is used as chip select during configuration transactions.                                                                                                                                                                                                                                                        |

| PERR#         | 19                                                                                                                    | 0            | Parity Error is used for reporting of data parity errors.                                                                                                                                                                                                                                                                                     |

| RST#          | 81                                                                                                                    | Ι            | PCI Reset. RST# may be asynchronous to CLK when asserted or deasserted.                                                                                                                                                                                                                                                                       |

| INTA#         | 80                                                                                                                    | 0            | Interrupt. This is level sensitive, active LOW and open drain output.                                                                                                                                                                                                                                                                         |

|               |                                                                                                                       | Intel Bus Mo | ode (Selected when CLK=HIGH)                                                                                                                                                                                                                                                                                                                  |

| CLK           | 84                                                                                                                    | Ι            | This pin must be pulled to HIGH.                                                                                                                                                                                                                                                                                                              |

| AD7-0         | 38,39,40,41,44,45<br>,46,47                                                                                           | I/O          | Multiplexed address and data. During the address phase, AD7-0 contain<br>a 8-bit physical address. During the data phase, AD7-AD0 contain data.                                                                                                                                                                                               |

| CS#                  | 12                          | Ι           | Chip select.                                                                                                    |  |  |

|----------------------|-----------------------------|-------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| ALE                  | 13                          | Ι           | Address Latch Enable. Used to latch addresses.                                                                  |  |  |

| RD#                  | 37                          | Ι           | Read.                                                                                                           |  |  |

| WR#                  | 22                          | Ι           | Write.                                                                                                          |  |  |

| RST#                 | 81                          | Ι           | Reset.                                                                                                          |  |  |

| INT#                 | 80                          | 0           | Interrupt. This is a level sensitive, active LOW and open drain output.                                         |  |  |

|                      | Me                          | otorola Bus | Mode (Selected when CLK=LOW)                                                                                    |  |  |

| CLK                  | 84                          | Ι           | This pin must be pulled to LOW.                                                                                 |  |  |

| D7-D0                | 38,39,40,41,44,45<br>,46,47 | I/O         | Data.                                                                                                           |  |  |

| A7-A0                | 7,8,9,10,33,34,35,<br>36    | Ι           | Address.                                                                                                        |  |  |

| CS#                  | 12                          | Ι           | Chip select.                                                                                                    |  |  |

| DS#                  | 22                          | Ι           | Data strobe.                                                                                                    |  |  |

| RW                   | 37                          | Ι           | Read/write identify. HIGH for read, and LOW for write.                                                          |  |  |

| RST#                 | 81                          | Ι           | Reset.                                                                                                          |  |  |

| INT#                 | 80                          | 0           | Interrupt. This is a level sensitive, active LOW and open drain output.                                         |  |  |

|                      |                             |             | GCI Bus                                                                                                         |  |  |

| DCL                  | 72                          | Ι           | GCI Bus Data Clock of the frequency: 1.536 MHz.                                                                 |  |  |

| FSC                  | 71                          | Ι           | GCI Bus Frame Synchronization Clock: 8KHz.                                                                      |  |  |

| DD                   | 70                          | I/O         | GCI Bus Data Downstream : Slave mode - input, master mode - output.                                             |  |  |

| DU                   | 69                          | I/O         | GCI Bus Data Upstream : Slave mode - output, master mode - input.                                               |  |  |

|                      |                             |             | PCM Interface                                                                                                   |  |  |

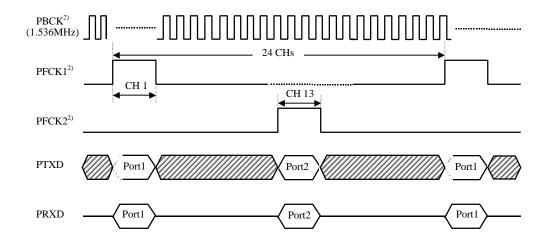

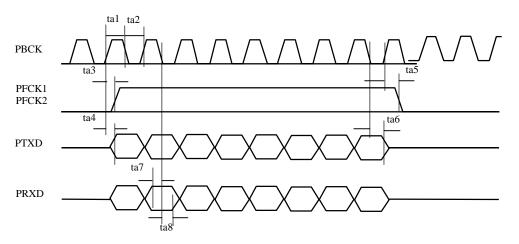

| PFCK1                | 64                          | 0           | PCM port 1 frame synchronization signal, with 8 KHz repetition rate<br>and 8 bit pulse width.                   |  |  |

| PFCK2                | 62                          | 0           | PCM port 2 frame synchronization signal, with 8 KHz repetition rate<br>and 8 bit pulse width.                   |  |  |

| PBCK                 | 63                          | 0           | PCM bit synchronization clock of 1.536 MHz.                                                                     |  |  |

| PTXD                 | 65                          | 0           | PCM transmit data output. A maximum of two channels with 64 Kbit/s data rate can be multiplexed on this signal. |  |  |

| PRXD                 | 66                          | Ι           | PCM receive data input. A maximum of two channels with 64 Kbit/s data rate can be multiplexed on this signal.   |  |  |

|                      | I                           | ISDN Sig    | nals and External Crystal                                                                                       |  |  |

| SR1                  | 49                          | I           | S/T bus receiver input (negative).                                                                              |  |  |

| SR2                  | 50                          | I           | S/T bus receiver input (negative).                                                                              |  |  |

| SX1                  | 54                          | 0           | S/T bus transmitter output (positive).                                                                          |  |  |

| SX2                  | 55                          | 0           | S/T bus transmitter output (negative).                                                                          |  |  |

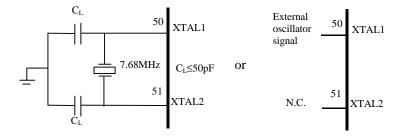

| XTAL1                | 56                          | Ι           | Crystal or Oscillator clock input. The clock frequency:<br>7.68MHz±100PPM.                                      |  |  |

| XTAL2                | 57                          | 0           | Crystal clock output. Left unconnected when using oscillator.                                                   |  |  |

|                      |                             | Extern      |                                                                                                                 |  |  |

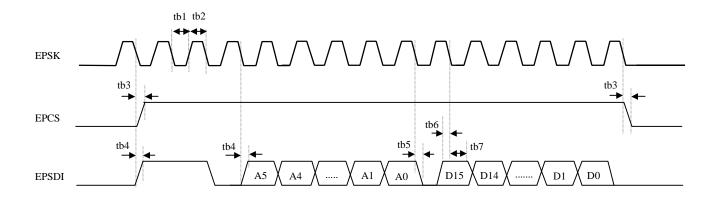

| EPCS                 | 73                          | 0           | Serial EEPROM chip select (active HIGH).                                                                        |  |  |

| EPSK                 | 73                          | 0           | Serial EEPROM data clock (clock frequency < 250 KHz).                                                           |  |  |

| EPSDI                | 76                          | I           | Serial EEPROM data input.                                                                                       |  |  |

| EPSDO                | 75                          | 0           | Serial EEPROM data output.                                                                                      |  |  |

| 21500                | 15                          | 0           | Functional Test                                                                                                 |  |  |

| TESTD                | 61                          | т           | Used to enable normal operation (1) or enter test mode (0).                                                     |  |  |

| TESTP                | 01                          | I           |                                                                                                                 |  |  |

| PCI Power Management |                             |             |                                                                                                                 |  |  |

| PME       | 60                               | 0   | Power Management Event Signal. Level triggered, active HIGH. Drive                                                                                             |

|-----------|----------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |                                  |     | a transistor to PME# in PCI slot.                                                                                                                              |

|           |                                  |     | Peripheral Control                                                                                                                                             |

| TOUT2     | 20                               | 0   | Timer 2 output. A square wave with 50 % duty cycle, 1~63 ms period can be generated.                                                                           |

| XINTIN0   | 52                               | Ι   | A level change (either direction) will generate a maskable interrupt on the PCI bus interrupt request pin INTA#.                                               |

| XINTIN1   | 53                               | Ι   | A level change (either direction) will generate a maskable interrupt on the PCI bus interrupt request pin INTA#.                                               |

| IO0-IO10  | 79,78,77,29,28,<br>27,26,4,3,2,1 | I/O | When confiured as simple IO mode (PCTL:XMODE = 0), these pins can read/write data from/to peripheral components. The pin directions are selected via register. |

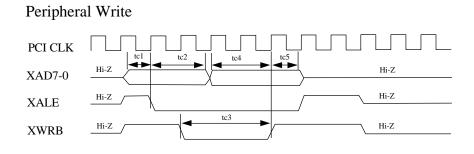

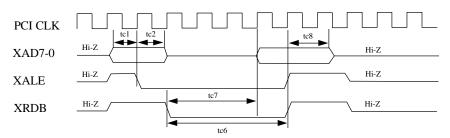

| XAD7-XAD0 | 29,28,27,26,<br>4,3,2,1          | I/O | When configured as microprocessor mode (PCTL:XMODE = 1), address and data are multiplexed on these pins.                                                       |

| XALE      | 77                               | 0   | When configured as microprocessor mode (PCTL:XMODE = 1), this is the Address Latch Enable output.                                                              |

| XRDB      | 78                               | 0   | When configured as microprocessor mode (PCTL:XMODE = 1), this is the read pulse.                                                                               |

| XWRB      | 79                               | 0   | When configured as microprocessor mode (PCTL:XMODE = 1), this is the write pulse.                                                                              |

|           | ·                                |     | Power and Ground                                                                                                                                               |

| VDDD      | 17,58,67,83                      | Ι   | Digital Power Supply (5V±5%).                                                                                                                                  |

| VDDA      | 51                               | Ι   | Analog Power Supply (5V±5%).                                                                                                                                   |

| VDDB      | 6,32,43,89                       | Ι   | PCI Bus Power Supply.                                                                                                                                          |

| VSSD      | 16,59,68,82                      | Ι   | Digital Ground.                                                                                                                                                |

| VSSA      | 48                               | Ι   | Analog Ground.                                                                                                                                                 |

| VSSB      | 5,31,42,88                       | Ι   | PCI Bus Ground.                                                                                                                                                |

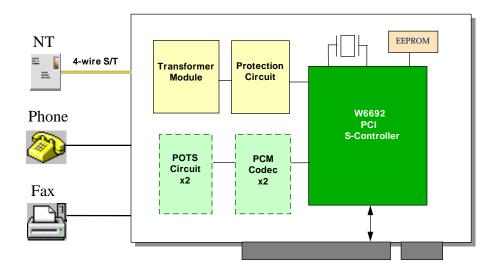

## 5. SYSTEM DIAGRAM AND APPLICATIONS

Typical applications include :

- PCI passive S-card for data only service

- PCI passive S-card with one handset/POTS connection

- PCI passive S-card with two POTS connections

- ISDN TA or other embedded application

The all-in-one characteristic of W6692 makes it excellent for passive ISDN PCI card. W6692 integrates three HDLC controllers in the chip and interfaces to PCI bus directly. In addition, W6692 provides peripheral control circuits for PCM CODEC and POTS interface.

In the following application, only a few TTL-like glue circuits are needed for the two POTS interface control.

W6692 also integrates the 8-bit Intel or Motorola microprocessor interface which makes it excellent for TA application.

#### FIG.5.1 ISDN INTERNET PASSIVE S-CARD WITH TWO POTS CONNECTIONS

# 6. BLOCK DIAGRAM

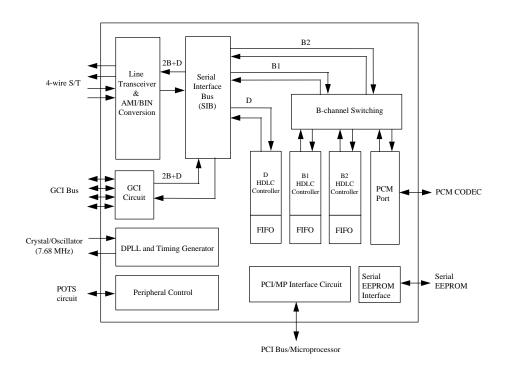

The block diagram of W6692 is shown in Figure 6.1

### FIG.6.1 W6692 FUNCTIONAL BLOCK DIAGRAM

# 7. FUNCTIONAL DESCRIPTIONS

#### 7.1 Main Block Functions

The functional block diagram of W6692 is shown in Fig.6.1. The main function blocks are :

- Layer 1 function according to ITU-T I.430

- Serial Interface Bus (SIB)

- B channel switching

- GCI bus interface

- PCM port and internal switching (x 2)

- D channel HDLC controller

- B channel HDLC controllers (x 2)

- PCI/microprocessor interface circuit

- Serial EEPROM interface for PCI Configuration purpose

- Peripheral control

The layer 1 function includes:

- S/T bus transmitter/receiver

- Timing recovery using Digital Phase Locked Loop (DPLL) circuit

- Layer 1 activation/deactivation

- D channel access control

- Frame alignment

- Multi-frame synchronization

- Test functions

The serial interface bus performs the multiplexing/demultiplexing of D and 2B channels.

The B channel switching determines the connection between layer1/GCI, layer 2 and PCM.

The GCI circuit is used to connect a U transceiver (slave mode) or other slave GCI device (master mode).

The PCM port provides two 64 kbps clear channels to connect to PCM codec chips and switching between two PCM ports.

The D channel HDLC controller performs the LAPD (Link Access Procedure on the D channel) protocol according to ITU-T I.441/Q.921 recommendation.

There are two independent B channel HDLC controllers. They can be used to support HDLC-like protocols such as Internet PPP. Two B channels are also handled by one HDLC controller to support OCN application.

The PCI interface circuit implements PCI specification revision 2.2 slave mode function. When PCI circuit is disabled, a 8-bit microprocessor interface is used to control the chip.

The peripheral control block is used to control other peripheral devices such as CODEC, SLIC, DTMF detector, LEDs.

#### 7.2 Layer 1 Functions Descriptions

The layer 1 functions includes :

- Transmitter/Receiver which conform to the electrical specifications of ITU-T I.430

- Receiver clock recovery and timing generation

- Output phase delay (deviation) compensation

- Layer 1 activation/deactivation procedures

- D channel access control

- Frame alignment

- Multi-frame synchronization

- Test functions

#### 7.2.1 S/T Interface Transmitter/Receiver

According to ITU-T I.430, pseudo-ternary code with 100% pulse width is used in both directions of transmission on the S/T interface. The binary "1" is represented by no line signal (zero volt), whereas a binary "0" is represented by a positive or negative pulse.

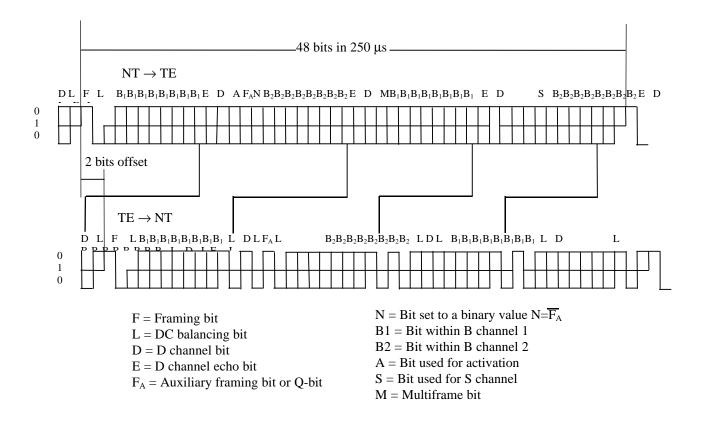

Data transmissions on the S/T interface are arranged as frame structures. The frame is 250  $\mu$ s long and consists of 48 bits, which corresponds to a 192 kbit/s line rate. Each frame carries two octets of B1 channel, two octets of B2 channel and four D channel bits. Therefore, the 2B+D data rate is 144 kbit/s. The frame structure is shown in Fig.7.1.

The frame begin is marked by a framing bit, which is followed by a DC balancing bit. The first binary "0" following the framing bit balancing bit is of the same polarity as the framing bit balancing bit, and subsequent binary zeros must alternate in polarity.

## FIG.7.1 FRAME STRUCTURE AT S/T INTERFACE

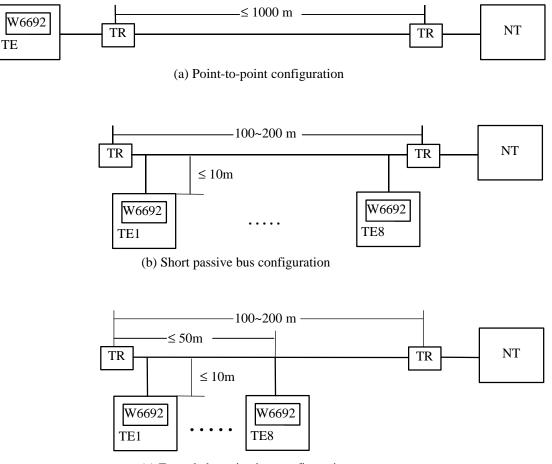

There are three wiring configurations according to I.430 : point-to-point, short passive bus and extended pass bus. They are shown in Fig.7.2.

# (c) Extended passive bus configuration

TR : Terminating Resistor

### FIG.7.2 W6692 WIRING CONFIGURATION IN TE APPLICATIONS

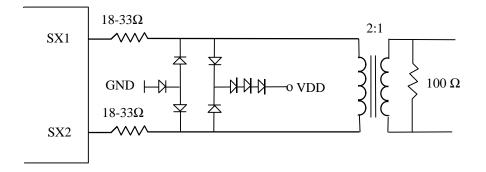

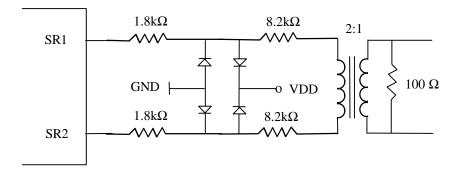

The transmitter and receiver are implemented by differential circuits to increase signal to noise ratio (SNR). The nominal differential line pulse amplitude at 100  $\Omega$  termination is 750 mV, zero to peak. Transformers with 2:1 turn ration are needed at transmitter and receiver for voltage level translation and DC isolation.

To meet the electrical characteristic requirements in I.430, some additional circuits are needed. At the transmitter side, the external resistors (18 to 33  $\Omega$ ) are used to adjust the output pulse amplitude and to meet the transmitter active impedance ( $\geq 20 \Omega$  when transmitting binary zeros). At the receiver side, the 1.8 k $\Omega$  resistors protect the device inputs , while the 10 k $\Omega$  resistors (1.8 k $\Omega$  +8.2 k $\Omega$ ) limit the peak current in impedance tests. The diode bridge is used for overvoltage protection.

#### FIG.7.3 EXTERNAL TRANSMITTER CIRCUITRY

#### FIG.7.4 EXTERNAL RECEIVER CIRCUITRY

After hardware reset, the receiver may enter power down state in order to save power consumption. In this state, the internal clocks are turned off, but the analog level detector is still active to detect signal coming from the S interface. The power down state is left either by non-INFO 0 signal from S interface or C/I command from microprocessor.

### 7.2.2 Receiver Clock Recovery And Timing Generation

A Digital Phase Locked Loop (DPLL) circuit is used to derive the receive clock from the received data stream. This DPLL uses a 7.68 MHz clock as reference. According to I.430, the transmit clock is normally delayed by 2 bit time from the receive clock. The "total phase deviation from input to output" is -7% to +15% of a bit period. In some cases, delay compensation may be needed to meet this requirement (see OPS1-0 bits in D\_CTL register).

| OPS1 | OPS0 | Effect                           |

|------|------|----------------------------------|

| 0    | 0    | No phase delay compensation      |

| 0    | 1    | Phase delay compensation 260 ns  |

| 1    | 0    | Phase delay compensation 520 ns  |

| 1    | 1    | Phase delay compensation 1040 ns |

### TABLE 7.1 OUTPUT PHASE DELAY COMPENSATION TABLE

W6692 does not need RC filter on receiver side, therefore zero delay compensation is selected normally. This is the default setting.

The PCM output clocks (PFCK1-2, PBCK) are synchronous to the S-interface timing.

#### 7.2.3 Layer 1 Activation/Deactivation

The layer 1 activation/deactivation procedures are implemented by a finite state machine. The state transitions are triggered by signals received at S interface or commands issued from microprocessor. The state outputs signals to S interface and indication to microprocessor. The CIX register is used by microprocessor to issue command, and the CIR register is used by microprocessor to receive indication.

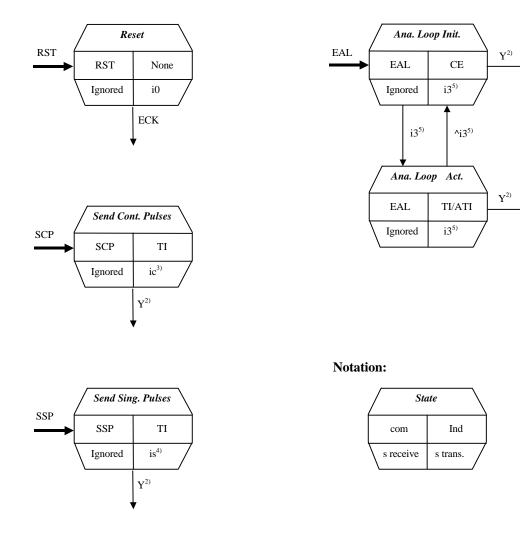

Some commands are used for special purposes. They are "layer 1 reset", "analog loopback", "send continuous zeros" and "send single zero".

#### 7.2.3.1 States Descriptions And Command/Indication Codes

#### F3 Deactivated without clock

This is the "deactivated" state of ITU-T I.430. The receive line awake unit is active except during a hardware reset pulse. After reset, once the indication "1111" has been read out, internal clocks will turn off and stay at this state if INFO 0 is received on the S line. The turn off time is approximate 93 ms. The ECK command must be issued to activate the clocks.

#### F3 Deactivated with clock

This state is identical to "F3 Deactivated without clock" except the internal clocks are enabled. The state is entered by the ECK command. The clocks are enabled approximately 0.5 ms to 4 ms after the ECK command, depending on the crystal capacitances. (It is about 0.5 ms for 12pF to 33pF capacitance).

#### F3 Awaiting Deactivation

The W6692 enters this state after receiving INFO 0 (in states F5 to F8) for 16ms (64 frames). This time constant prevents spurious effect on S interface. Any non-INFO 0 signal on the S interface causes transition to "F5 Identifying Input" state. If this transition does not occur in a specific time (500 - 1000 ms), the microprocessor may issue DRC or ECK command to deactivate layer 1.

#### F4 Awaiting Signal

This state is reached when an activate request command has been received. In this state, the layer 1 transmits INFO1 and INFO 0 is received from the S interface. The software starts timer T3 of I.430 when issuing activate request command. The software deactivates layer 1 if no signal other than INFO 0 has been received on S interface before expiration of T3.

#### F5 Identifying Input

After the receipt of any non-INFO 0 signal from NT, the W6692 ceases to transmit INFO 1 and awaits identification of INFO 2 or INFO 4. This state is reached at most 50  $\mu$ s after a signal different from INFO 0 is present at the receiver of the S interface.

#### F6 Synchronized

When W6692 receives an activation signal (INFO 2), it responds with INFO 3 and waits for normal frames (INFO 4). This state is reached at most 6 ms after an INFO 2 arrives at the S interface (in case the clocks were disabled in "F3 Deactivated without clock").

#### F7 Activated

This is the normal active state with the layer 1 protocol activated in both directions. From state "F6 Synchronized", state F7 is reached at most 0.5 ms after reception of INFO 4. From state "F3 Deactivated without clock" with the clocks disabled, state F7 is reached at most 6 ms after the W6692 is directly activated by INFO 4.

#### F8 Lost Framing

This is the state where the W6692 has lost frame synchronization and is awaiting resynchronization by INFO 2 or INFO 4 or deactivation by INFO 0.

#### **Special States:**

#### **Analog Loop Initiated**

On Enable Analog Loop command, INFO 3 is sent by the line transmitter internally to the line receiver (INFO 0 is sent to the line). The receiver is not yet synchronized.

#### **Analog Loop Activated**

The receiver is synchronized on INFO 3 which is looped back internally from the transmitter. The indication "TI" or "ATI" is sent depending on whether or not a signal different from INFO 0 is detected on the S interface.

#### Send Continuous Pulses

A 96 kHz continuous pulse with alternating polarities is sent.

#### Send Single Pulses

A 2 KHz , isolated pulse with alternating polarities is sent.

#### Layer 1 Reset

A layer 1 reset command forces the transmission of INFO 0 and disables the S line awake detector. Thus activation from NT is not possible. There is no indication in reset state. The reset state can be left only with ECK command.

| Command                         | Symbol | Code | Description                                            |

|---------------------------------|--------|------|--------------------------------------------------------|

| Enable clock                    | ECK    | 0000 | Enable internal clocks                                 |

| Layer 1 reset                   | RST    | 0001 | Layer 1 reset                                          |

| Send continuous pulses          | SCP    | 0100 | Send continuous pulses at 96 kHz                       |

| Send single pulses              | SSP    | 0010 | Send isolated pulses at 2 kHz                          |

| Activate request at priority 8  | AR8    | 1000 | Activate layer 1 and set D channel priority level to 8 |

| Activate request at priority 10 | AR10   | 1001 | Activate layer 1 and set D channel priority to 10      |

| Enable analog loopback          | EAL    | 1010 | Enable analog loopback                                 |

| Deactivate layer 1              | DRC    | 1111 | Deactivate layer 1 and disable internal clocks         |

### TABLE 7.2 LAYER 1 COMMAND CODES

## **TABLE 7.3 LAYER 1 INDICATION CODES**

| Indication                        | Symbol | Code | Descriptions                                                  |

|-----------------------------------|--------|------|---------------------------------------------------------------|

| Clock Enabled                     | CE     | 0111 | Internal clocks are enabled                                   |

| Deactivate request downstream     | DRD    | 0000 | Deactivation request by S interface, i.e INFO 0 received      |

| Level detected                    | LD     | 0100 | Signal received, receiver not synchronous                     |

| Activate request downstream       | ARD    | 1000 | INFO 2 received                                               |

| Test indication                   | TI     | 1010 | Analog loopback activated or continuous zeros or single zeros |

|                                   |        |      | transmitted                                                   |

| Awake test indication             | ATI    | 1011 | Level detected during test function                           |

| Activate indication with priority | AI8    | 1100 | INFO 4 received, D channel priority is 8 or 9                 |

| class 1                           |        |      |                                                               |

| Activate indication with priority | AI10   | 1101 | INFO 4 received, D channel priority is 10 or 11               |

| class 2                           |        |      |                                                               |

| Clock disabled                    | CD     | 1111 | Layer 1 deactivated, internal clocks are disabled             |

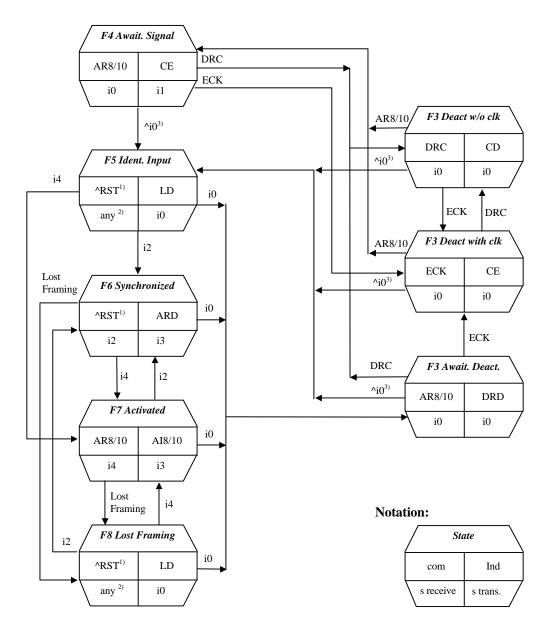

### 7.2.3.2 State Transition Diagrams

The followings are the state transition diagrams, which implement the activation/deactivation state matrix in I.430 (TABLE 5/I.430). The "command" and "s receive" entries in each state octagon keep the state, the "indication" and "s transmit" entries in

each state octagon are the state outputs. For example, at "F3 Deactivated with clock" state, the layer 1 will stay at this state if the command is "ECK" and the INFO 0 is received on S interface. At this state, it provides "CE" indication to the microprocessor and transmits INFO 0 on S interface. The "AR8/10" command causes transition to F4 and non-INFO 0 signal causes transition to F5. Note that the command code writtern by the microprocessor in CIX register and indication code written by layer 1 in CIR register are transmitted repeatedly until a new code is written.

Note:

1. "^RST" means "NOT layer 1 reset command".

2. "Any" means any signal other than i0, which has not yet been determined.

3. "^i0" means any signal other than i0.

### FIG.7.5 LAYER 1 ACTIVATION/DEACTIVATION STATE DIAGRAM - NORMAL MODE

#### Note :

- 1. RST can be issued at any state, while SCP, SCZ and EAL can be issued only at F3 or F7.

- 2. Y is one of the commands : ECK, DRC, RST.

- 3. Continuous pulses at 96 kHz.

- 4. Isolated pulses at 2 kHz.

- 5. The INFO 3 is transmitted internally only.

# FIG.7.6 LAYER 1 ACTIVATION/DEACTIVATION STATE DIAGRAM - SPECIAL MODE

### 7.2.4 D Channel Access Control

The D channel access control includes collision detection and priority management. The collision detection is always enabled. The priority management procedure as specified in ITU-T I.430 is fully implemented in W6692.

A collision is detected if the transmitted D bit and the received echo bit do not match. When this occurs, D channel transmission is immediately stopped and the echo channel is monitored to attempt the next D channel access. The layer 1 module uses an internal signal to inform layer 2 module of the collision condition (DRDY bit goes inactive in D\_XSTA register).

There are two priority classes: class 1 and class 2. Within each class, there are normal and lower priority levels.

### **TABLE 7.4 D PRIORITY CLASSES**

|                     | Normal level | Lower level |

|---------------------|--------------|-------------|

| Priority class<br>1 | 8            | 9           |

| Priority class<br>2 | 10           | 11          |

The selection of priority class is via the AR8/AR10 command. The following table summarizes the commands/indications used for setting the priority classes:

#### **TABLE 7.5 D PRIORITY COMMANDS/INDICATIONS**

| Command                              | Symbol | Code | Remarks                                          |

|--------------------------------------|--------|------|--------------------------------------------------|

| Activate request, set priority 8     | AR8    | 1000 | Activation command, set D channel priority to 8  |

| Activate request, set priority 10    | AR10   | 1001 | Activation command, set D channel priority to 10 |

| Indication                           | Abbr.  |      | Remarks                                          |

| Activate indication with priority 8  | AI8    | 1100 | Info 4 received, D channel priority is 8 or 9    |

| Activate indication with priority 10 | AI10   | 1101 | Info 4 received, D channel priority is 10 or 11  |

#### 7.2.5 Frame Alignment

The following sections describe the behavior of W6692 in respect to the CTS-2 conformance test procedures for frame alignment. Please refer to ETSI-TM3 Appendix B1 for detailed descriptions.

### 7.2.5.1 FAinfA\_1fr

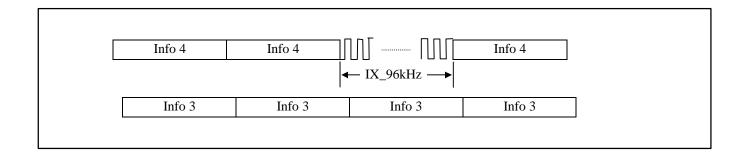

This test checks if TE does not lose frame alignment on receipt of one bad frame. The pattern for the bad frame is defined as IX\_96 kHz. This pattern consists of alternating pulses at 96 kHz during the whole frame.

| Device | Settings | Result |

|--------|----------|--------|

| W6692  | None     | Pass   |

## 7.2.5.2 FAinfB\_1fr

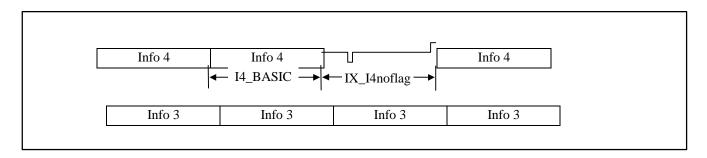

This test checks if TE does not lose frame alignment on receipt of one IX\_I4noflag frame which has no framing and balancing bit. The following figure indicates one possible IX\_I4noflag waveform.

| Device | Settings | Result |

|--------|----------|--------|

| W6692  | None     | Pass   |

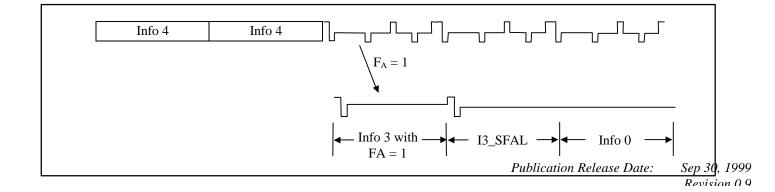

# 7.2.5.3 FAinfD\_1fr

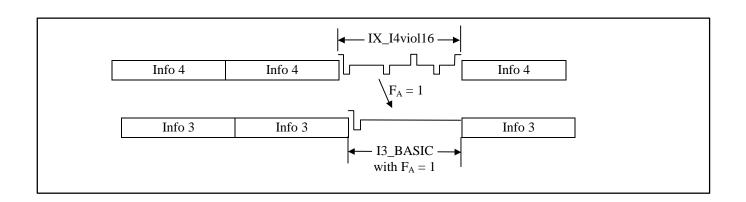

This test checks if TE does not lose frame alignment on receipt of one IX-I4viol16 frame. The IX\_I4viol16 frame remains at binary "1" until the first B2 bit which is bit position 16. The pulse sequences are: Framing bit, balancing bit, B2 bit, M bit, S bit, balancing bit. The TE should reflect the received  $F_A$  bit ( $F_A$ ="1") in the transmitted frame.

| Device | Settings | Result |

|--------|----------|--------|

| W6692  | None     | Pass   |

## 7.2.5.4 FAinfA\_kfr

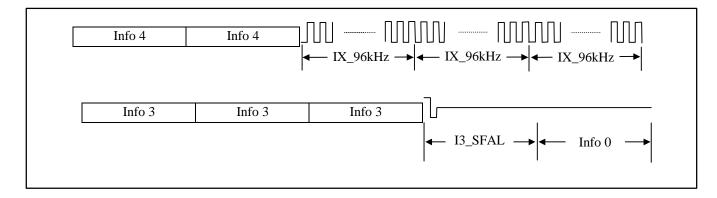

This is to test the number k of IX\_96 kHz frames necessary for loss of frame alignment.

| Device | Settings | Result |

|--------|----------|--------|

| W6692  | k =2     | Pass   |

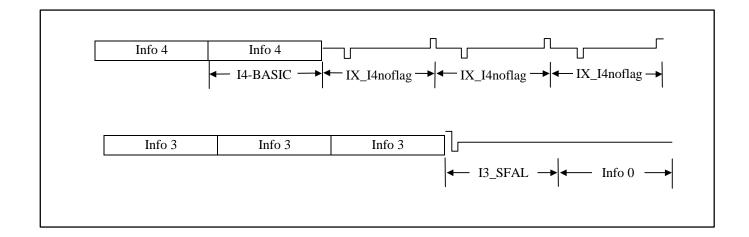

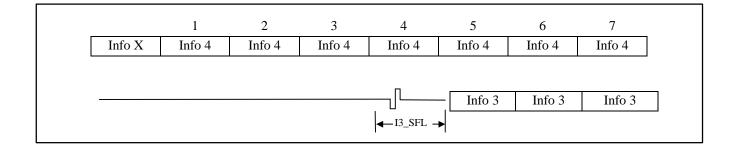

### 7.2.5.5 FAinfB\_kfr

This is to test the number k of IX\_I4noflag frames necessary for loss of frame alignment.

| Device | Settings | Result |

|--------|----------|--------|

| W6692  | k =2     | Pass   |

## 7.2.5.6 FAinfD\_kfr

This is to test the number k of IX\_I4noflag frames necessary for loss of frame alignment.

Info 3 Info 3

# W6692 PCI ISDN S/T-Controller

| Device | Settings | Result |

|--------|----------|--------|

| W6692  | k = 2    | Pass   |

### 7.2.5.7 Faregain

This is to test the number m of good frames necessary for regain of frame alignment. The TE regains frame alignment at m+1 frame.

The W6692 achieves synchronization after 5 frames, i.e m=4.

| Device | Settings | Result |

|--------|----------|--------|

| W6692  | m = 4    | Pass   |

### 7.2.6 Multiframe Synchronization

As specified by ITU-T I.430, the Q bit is transmitted from TE to NT in the position normally occupied by the auxiliary framing bit ( $F_A$ ) in one frame out of 5, whereas the S bit is transmitted from NT to TE. The S and Q bit positions and multiframe structure are shown in Table 7.6.

The functions provided by W6692 are:

- Multiframe synchronization: Synchronization is achived when the M bit pattern has been correctly received during 20 consecutive frames starting from frame number 1.

Note: Criterion for multiframe synchronization is not defined in I.430 Recommendation.

- S bits receive and detect: When synchronization is achieved, the four received S bits in frames 1,6,11,16 are stored as S1 to S4 in the SQR register respectively. A change in the recived four bits (S1-4) is indicated by an interrupt (ISC in D\_EXIR register and SCC in CIR register).

- Multiframe synchronization monitoring: Multiframe synchronization is constantly monitored. The synchronization state is indicated by the MSYN bit in the SQR register.

- Q bits transmit and  $F_A$  mirroring: When multiframe synchronization is achived, the four bits Q1-4 stored in the SQXR register are transmitted as the four Q bits ( $F_A$ -bit position) in frames 1,6,11 and 16. Otherwise the  $F_A$  bit transmitted is a mirror of the received  $F_A$ -bit. At loss of synchronization, the mirroring is resumed at the next  $F_A$ -bit.

- The multiframe synchronization can be disabled by setting MFD bit in the D\_MODE register.

- According to I.430 Recommendation, the S/Q channel can be used as operation and maintenance signalling channel. At transmitter, a S/Q code for a message shall be repeated at least six times or as many as necessary to obtain the desired response. At receiver, a message shall be considered received only when the proper codes is received three consecutive times.

| Frame Number | NT-to-TE                     | NT-to-TE | NT-to-TE   | TE-to-NT                     |

|--------------|------------------------------|----------|------------|------------------------------|

|              | F <sub>A</sub> -bit position | M bit    | S bit      | F <sub>A</sub> -bit position |

| 1            | ONE                          | ONE      | S1         | Q1                           |

| 2            | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 3            | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 4            | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 5            | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 6            | ONE                          | ZERO     | S2         | Q2                           |

| 7            | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 8            | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 9            | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 10           | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 11           | ONE                          | ZERO     | <b>S</b> 3 | Q3                           |

| 12           | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 13           | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 14           | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 15           | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 16           | ONE                          | ZERO     | S4         | Q4                           |

| 17           | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 18           | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 19           | ZERO                         | ZERO     | ZERO       | ZERO                         |

| 20           | ZERO                         | ZERO     | ZERO       | ZERO                         |

### TABLE 7.6 Multiframe structure in S/T interface

| 1    | ONE  | ONE  | S1   | Q1   |

|------|------|------|------|------|

| 2    | ZERO | ZERO | ZERO | ZERO |

| etc. |      |      |      |      |

|      |      |      |      |      |

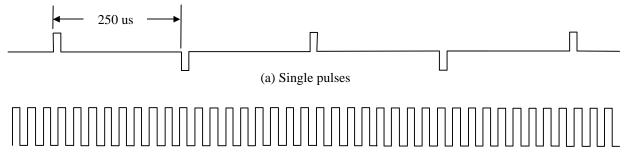

### 7.2.7 Test Functions

The W6692 provides loop and test functions as follows:

- Digital loop via DLP bit in D\_MODE register: In the layer 2 block, the transmitted 2B+D data are internally looped (from HDLC transmitter to HDLC receiver), and in the PCM ports, the transmitted B channels are internally looped (from PCM inputs to PCM outputs). The clock timings are generated internally and are independent of the S bus timing. This loop function is used for test of PCM and higher layer functions, excluding layer 1. After hardware reset, W6692 will power down if S bus is not connected or if there is no signal on the S bus. In this case, the C/I command ECK must be issued to power up the chip.

- Analog loop via the C/I command EAL: The analog S interface transmitter is internally connected to the S interface receiver. When the receiver has synchronized itself to the internal INFO 3 signal, the message "Test Indication" or "Awake Test Indication" is delivered to the CIR register. No signal is transmitted over the S interface.

In this mode, the S interface awake detector is enabled. Therefore if a level (INFO 2/ INFO 4) is detected on the S interface, this will be reported by the "Awake Test Indication (ATI)" indication.

- Remote loopback via RLP bit in D\_MODE register: The digital 2B data received from the S interface receiver is loopbacked to the S interface transmitter. The D channel is not looped. When RLP is enabled, layer 1 D channel is connected to HDLC port and DLP cannot be enabled.

- Transmission of special test signals via layer 1 command:

\* Send Single Pulses (SSP): To send isolated single pulses of alternating polarity, with pulse width of one bit time, 250 us apart, with a repetition frequency of 2 kHz.

\* Send Continuous Pulses (SCP): To send continuous pulses of alternating polarity, with pulse width of bit time. The repetition frequency is 96 kHz.

#### (b) Continuous pulses

FIG.7.7 SSP AND SCP TEST SIGNALS

### 7.3 Serial Interface Bus

The 192 kbps S/T interface signal consists of two B channels (64 kbps each), one D channel (16 kbps) and other control signals. The multiplexing/demultiplexing functions are carried out in the Serial Interface Bus (SIB) block. In addition, the B1 and B2 channels can be individually set to carry 64 kbps or 56 kbps traffic.

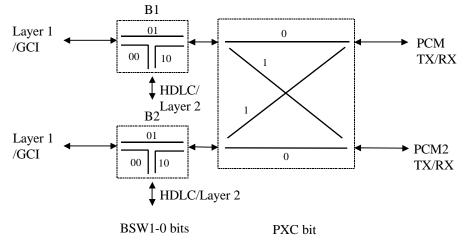

### 7.4 B Channel Switching

Each B channel in S/T bus or U transceiver can be individually programmed to connect to one of the three data ports : B channel HDLC controller , PCM port 1 or PCM port 2. In addition, the PCM ports can be programmed to connect to the B channel HDLC controller for voice recording/ retrieving from main memory in answering machine applications. In this case, only extended transparent mode can be used.

The switching matrix is controlled by PXC bit in PCTL register and BSW1-0 bits in B1\_MODE and B2\_MODE registers as follows :

A special mode is provided (BSW1-0 = 11B) in which case the PCM port can receive data from layer 1 and the HDLC receiver can receive data from PCM port simultaneously. Here are the setting values of possible switching combinations shown as below.

|     | PCM1       | Receive Table |         |

|-----|------------|---------------|---------|

| PXC | B1_SW[1:0] | B2_SW[1:0]    | PCM1 Rx |

| 0   | 00         | XX            | L1_B1   |

| 0   | 01         | XX            | L1_B1   |

| 0   | 10         | XX            | L2_B1   |

| 0   | 11         | XX            | PCM1    |

| 1   | XX         | 00            | L1_B2   |

| 1   | XX         | 01            | L1_B2   |

| 1   | XX         | 10            | L2_B2   |

| 1   | XX         | 11            | PCM2    |

| PXC | B1_SW[1:0]  | B2_SW[1:0] | PCM2 Rx |

|-----|-------------|------------|---------|

| IAC | D1_3 w[1.0] |            |         |

| 0   | XX          | 00         | L1_B2   |

| 0   | XX          | 01         | L1_B2   |

| 0   | XX          | 10         | L2_B2   |

| 0   | XX          | 11         | PCM2    |

| 1   | 00          | XX         | L1_B1   |

| 1   | 01          | XX         | L1_B1   |

| 1   | 10          | XX         | L2_B1   |

| 1   | 11          | XX         | PCM1    |

#### DCM2 D . Tabl

#### Layer2-B1 Receive Table

| PXC | B1_SW[1:0] | B2_SW[1:0] | L2_B1 Rx |

|-----|------------|------------|----------|

| х   | 00         | XX         | L1_B1    |

| х   | 01         | XX         | L1_B1    |

| 0   | 10         | XX         | PCM1     |

| 1   | 10         | XX         | PCM2     |

| х   | 11         | XX         | L1_B1    |

#### Layer2-B2 Receive Table

| PXC | B1_SW[1:0] | B2_SW[1:0] | L2_B2 Rx |

|-----|------------|------------|----------|

| х   | XX         | 00         | L1_B2    |

| х   | XX         | 01         | L1_B2    |

| 0   | XX         | 10         | PCM2     |

| 1   | XX         | 10         | PCM1     |

| х   | XX         | 11         | L1_B2    |

#### Layer1-B1 Receive Table

| PXC | B1_SW[1:0] | B2_SW[1:0] | L1_B1 Rx |

|-----|------------|------------|----------|

| х   | 00         | XX         | L2_B1    |

| 0   | 01         | XX         | PCM1     |

| 1   | 01         | XX         | PCM2     |

| Х   | 10         | XX         | High     |

| х   | 11         | XX         | L2_B1    |

#### Layer1-B2 Receive Table

| PXC | B1_SW[1:0] | B2_SW[1:0] | L1_B2 Rx |

|-----|------------|------------|----------|

| Х   | XX         | 00         | L2_B2    |

| 0   | XX         | 01         | PCM2     |

| 1   | XX         | 01         | PCM1     |

| х   | XX         | 10         | High     |

| Х   | XX         | 11         | L2_B2    |

# 7.5 PCM Port

There are two PCM ports in W6692. Each PCM port can connect to a PCM codec filter chip. These two PCM ports share the same signals except for the frame synchronization clocks. The frame synchronization clocks (PFCK1-2) are 8 kHz and the bit synchronization clock (PBCK) is 1.536 MHz. The bit data rate is 64 kbps per port.

### 7.6 D Channel HDLC Controller

There are two HDLC protocols that are used for ISDN layer 2 functions : LAPD and LAPB. Their frame formats are shown below.

#### LAPB modulo 8 :

| flag      | address  | control  | information     | FCS        | flag      |

|-----------|----------|----------|-----------------|------------|-----------|

| (1 octet) | (loctet) | (loctet) | (0 or N octets) | (2 octets) | (1 octet) |

| Control field bits | 7 | 6    | 5 | 4   | 3 | 2    | 1 | 0 |

|--------------------|---|------|---|-----|---|------|---|---|

| I frame            |   | N(R) |   | Р   |   | N(S) |   | 0 |

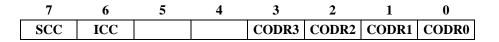

| S frame            |   | N(R) |   | P/F | S | S    | 0 | 1 |